38ur.com

38ur.com

2024年9月26日,佳能公司晓谕,已于9月26日向总部位于好意思国德克萨斯州的半导体定约——德克萨斯电子磋议所(TIE)运载其最先进的纳米压印光刻(NIL)系统FPA-1200NZ2C。

绫 丝袜在2023年10月13日,佳能雅致发布了大众首款NIL系统FPA-1200NZ2C,成为了大众首个将接受NIL时候的半导体制造系统贸易化的公司,该时候以不同于传统投影曝光时候的措施形成电路图案。

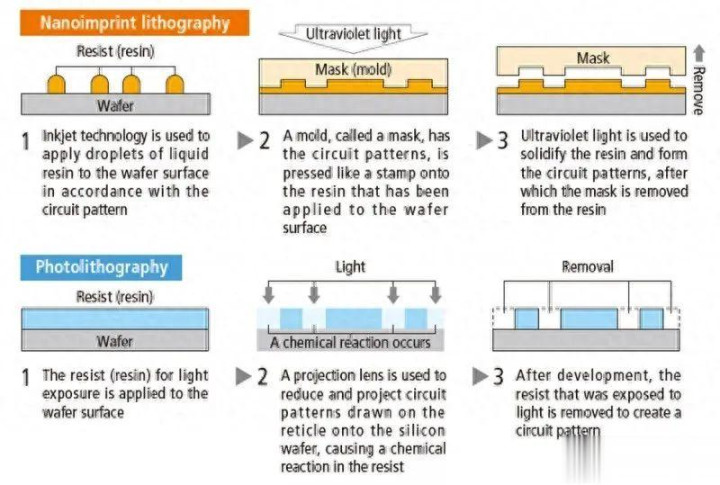

传统的光刻斥地通过将电路图案投射到涂有光刻胶的晶圆上来滚动电路图案,而新址品通过将印有电路图案的掩模像邮票相似压入晶圆上的光刻胶来杀青。由于它的电路图案滚动流程不经过光学机构,因此不错在晶圆上针织地再现掩模上的精致电路图案。新系统裁汰了功耗和资本,可杀青最小线宽为14nm的图形化,相配于5nm节点。

38ur.com

38ur.com

当下的5nm制程的先进半导体制造斥地市集,则由ASML的EUV光刻机所把持,单台价钱约1.5亿好意思元。关于接下来更为先进的2nm及以下制程的芯片,ASML也推出了资本更为腾贵的High-NAEUV光刻机,单台价钱高达3.5亿欧元,这也使得顶端制程所需的资本越来越高。

比较之下,佳能的当今NIL时候将不错使得芯片制造商不依赖于EUV光刻机就能坐褥最小5nm制程节点的逻辑半导体。佳能半导体斥地业务部长岩本和德此前还曾默示,要是纠正光罩,NIL致使不错坐褥2nm先进制程的芯片。佳能的纳米压印时候大约将有契机匡助佳能减弱其与ASML的差距。

更为要道的是,佳能的纳米压印斥地资本和制形资本王人远低于ASML的EUV光刻机。岩本和德默示,客户的资本因条目而异,据估算1次压印工序所需要的资本,无意能降至传统曝光斥地工序的一半。况兼,因为纳米压印斥地的规模较小,在研发等用途方面也更容易引进。据了解,接受纳米压印时候,将可使得举座的斥地投资裁汰至EUV光刻产线斥地的40%水平。

诚然佳能并未公布其纳米压印斥地的订价,关联词,佳能CEO御手洗富士夫此前曾默示,该公司的纳米压印斥地的“价钱将比ASML的EUV光刻机低一位数(即仅有10%)”。

凭据佳能最新的官方新闻稿裸露,其首台FPA-1200NZ2C将在TIE被用于先进半导体的研发和原型的坐褥。

据先容,TIE是一个半导体定约,确立于2021年,得回了德克萨斯大学奥斯汀分校的撑握。它由州和所在政府、半导体公司、国度磋议机构和其他实体构成。TIE提供对半导体研发计算和原型筹商要领的绽放考察,以匡助贬责与先进半导体时候(包括先进封装时候)关连的问题。

不外,需要指出的是,NIL是十足不同于光刻时候的全新旅途,因此它与现存的基于DUV或EUV光刻的产线是不兼容的,也即是说现存的大型芯片制造商无法再现存产线中径直使用NIL时候,需要重新耕种全新的坐褥线,显着这将成为辞谢NIL时候履行的一个成分。这也使得佳能的NIL斥地的初期的客户主要开首于磋议机构、科研院校等。

另外,联系于领少见十层不同电路结构的逻辑半导体来说,存储芯片由于存在多层近似的电路,更符合诈骗NIL时候来进行制造,这亦然为什么此前别传SK海力士、铠侠、好意思光等存储芯片厂商王人对NIL斥地感敬爱的原因。

佳能默示38ur.com,其将持续鼓励使用纳米压印光刻系统进行半导体制造的磋议和开发,为半导体制造时候的发展作念出孝敬。